TUGAS PRAKTIKUM SISTEM DIGITAL

MODUL III

GERBANG PEMBANGUN UNIVERSAL

MODUL III

GERBANG PEMBANGUN UNIVERSAL

Disusun oleh :

Andika Arif Fauzi

123090179

Plug 2

Asisten : Jefri Senoaji

Teknik Informatika Fakultas Teknologi Industri

Universitas Pembangunan Nasional [“Veteran”] Yogyakarta

2011

TUGAS

1. Buat rangkaian dan table kebenaran dari gambar dibawah ini :

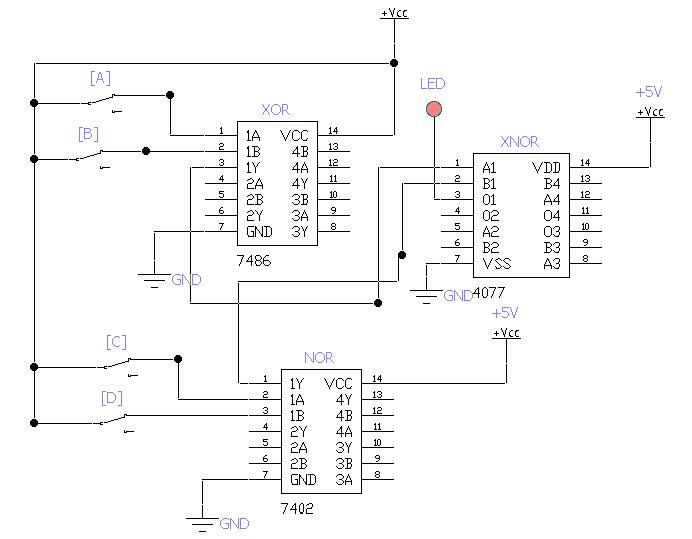

Skema Pengkabelan

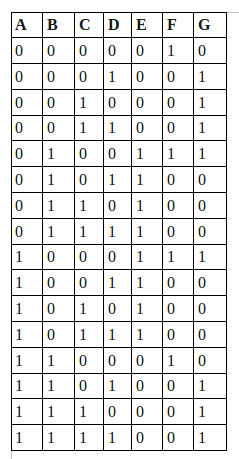

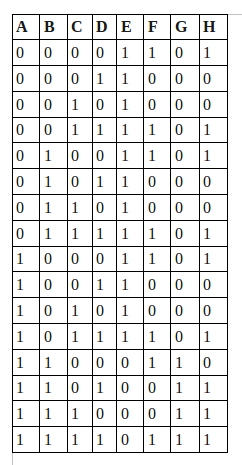

Tabel Kebenaran

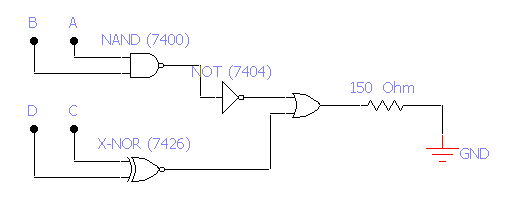

1. Buat rangkaian dan table kebenaran dari gambar dibawah ini :

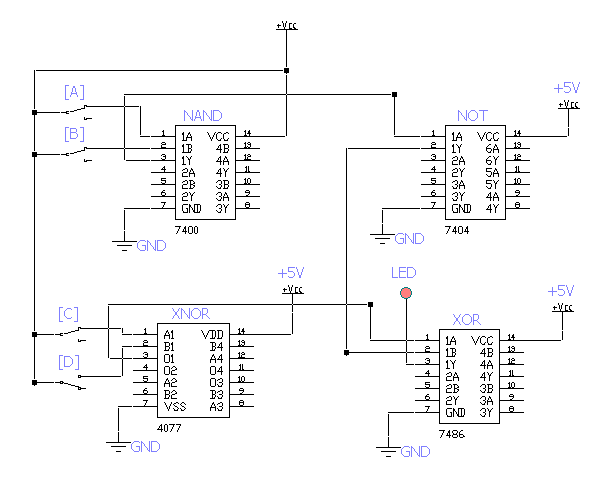

Skema Pengkabelan

Tabel Kebenaran

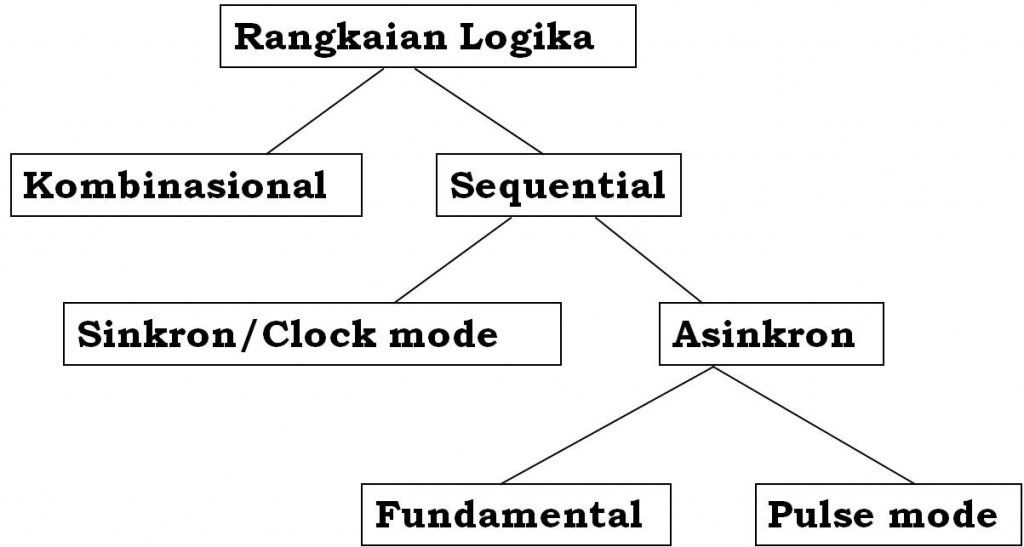

RANGKAIAN LOGIKA KOMBINASIONAL

Suatu rangkaian diklasifikasikan sebagai kombinasional jika memiliki sifat yaitu keluarannya ditentukan hanya oleh masukkan eksternal saja.

Suatu rangkaian diklasifikasikan sequential jika ia memiliki sifat keluarannya ditentukan oleh tidak hanya masukkan eksternal tetapi juga oleh kondisi sebelumnya.

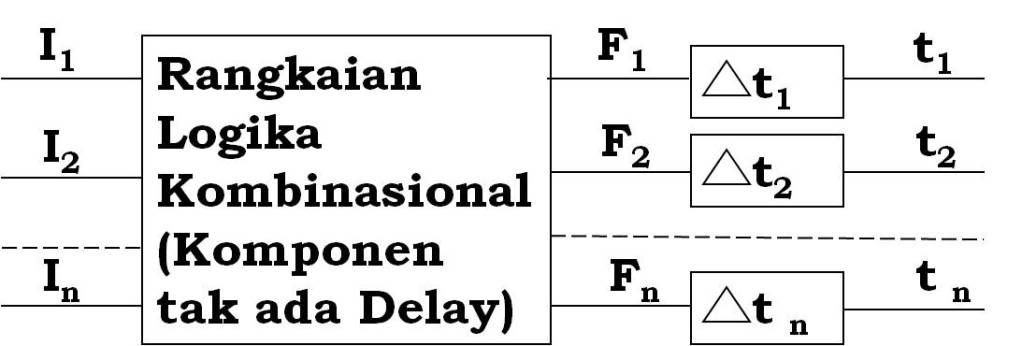

MODEL RANGKAIAN KOMBINASIONAL

PROSEDUR PERANCANGAN

a. Pokok permasalahan sudah ditentukan yaitu jumlah input yang dibutuhkan serta jumlah output yang tertentu.

b. Susun kedalam tabel kebenaran (Truth Table).

c. Kondisi don’t care dapat diikut sertakan apabila tidak mempengaruhi output.

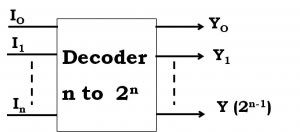

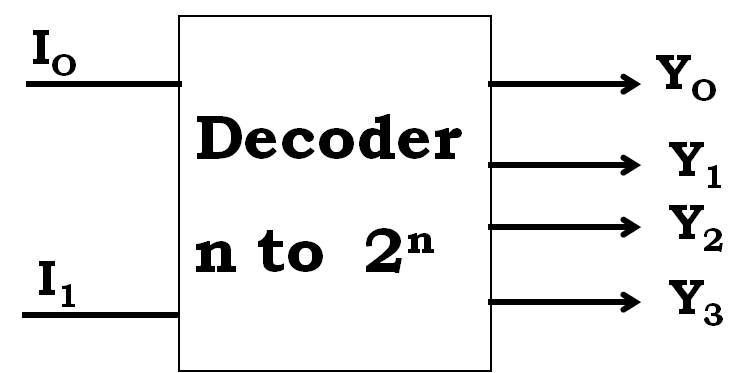

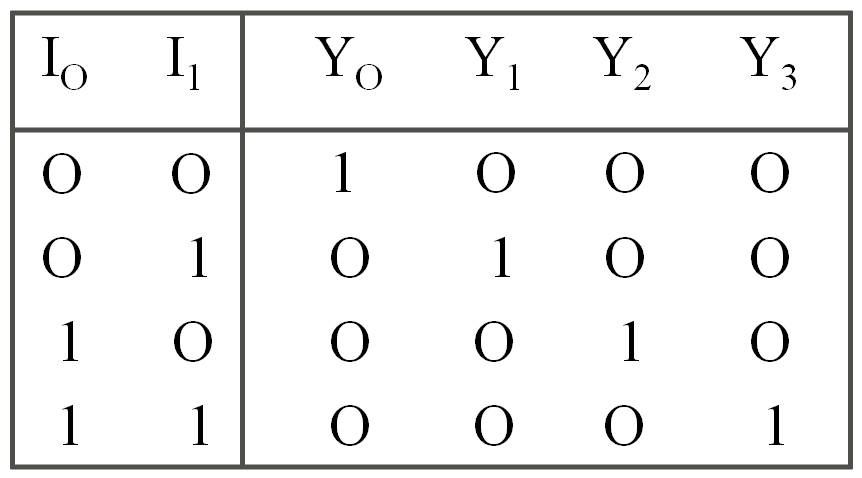

DECODER

Decoder adalah rangkaian kombinasi yang akan memilih salah satu keluaran sesuai dengan konfigurasi input. Decoder memiliki n input dan 2^n output.

TABEL KEBENARAN

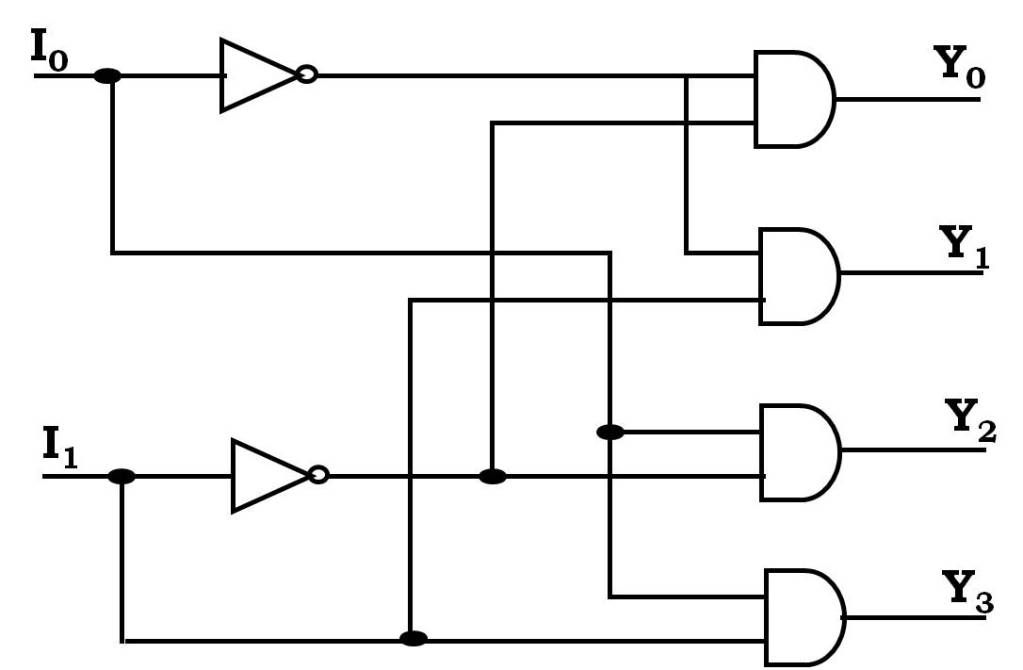

RANGKAIAN LOGIKA

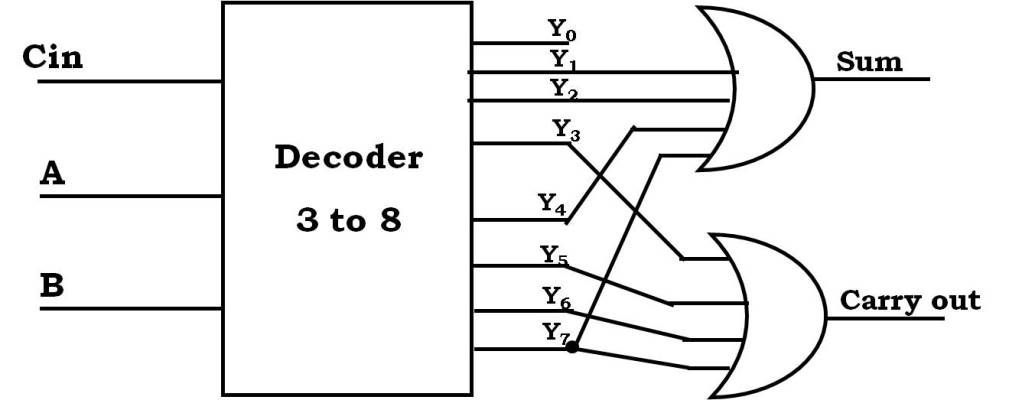

Untuk merancang rangkaian kombinasional dapat digunakan Decoder dan eksternal OR gate (rangkaian kombinasi n – input dan m– output dapat diimplementasikan dengan n to 2^n line decoder dan m – OR gate).

Contoh.

Implementasikan suatu Full Adder dengan memakai Decoder dan 2 gerbang OR

GAMBAR RANGKAIAN 3 TO 8

Jawab :

Sum = A + B + Cin = ? 1,2,4,7

Carry out = (A + B) Cin + AB = ? 3,5,6,7

ENCODER

Encoder adalah rangkaian kombinasi yang merupakan kebalikan dari Decoder yaitu manghasilkan output kode biner yang berkorespondensi dengan nilai input. Encoder memiliki 2^n input dan n output.

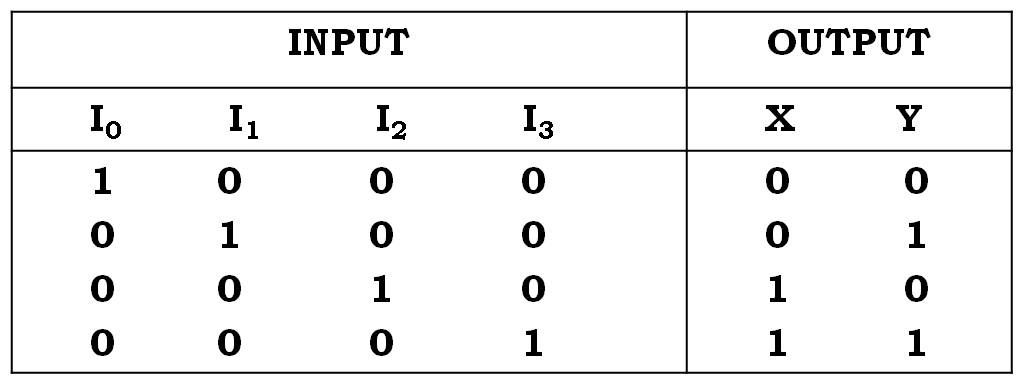

TABEL KEBENARAN ENCODER 4 TO 2

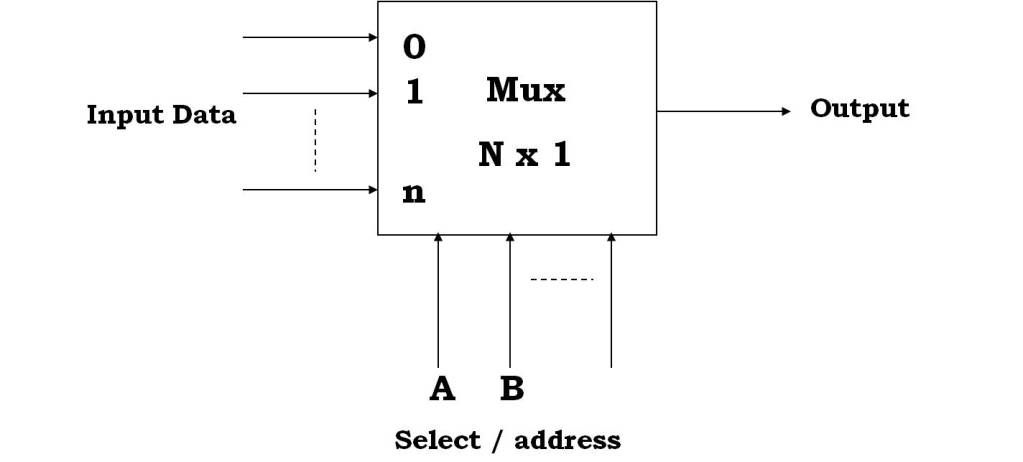

MULTIPLEXER (MUX)

BLOK DIAGRAM LOGIKA MUX

TABEL KEBENARAN

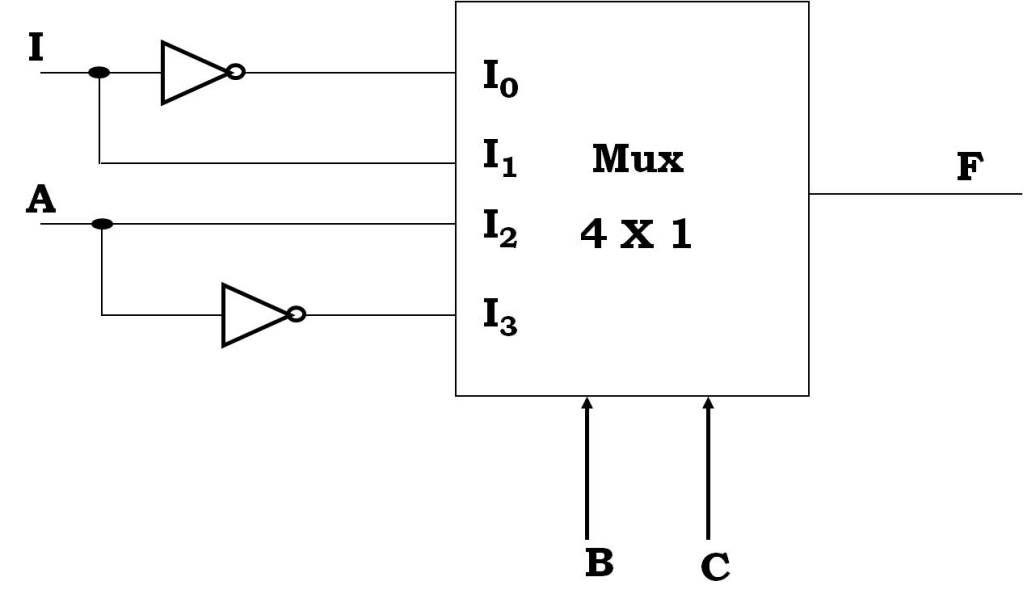

PROSEDUR PERANCANGAN RANGKAIAN KOMBINASIONAL DENGAN MUX

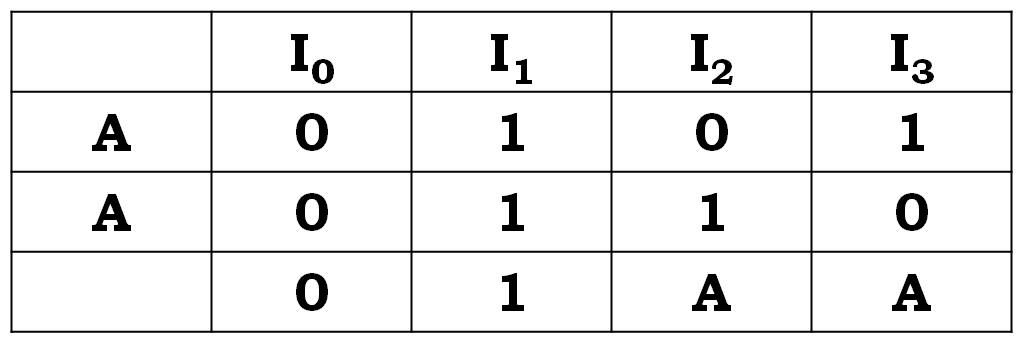

1. Buat tabel kebenaran sesuai dengan kondisi input dan output serta nomor Mintermnya.

2. Salah satu variabel input digunakan sebagai Data dan sisanya dari variabel input sebagai address/selector.

3. Buat tabel Implementasi dan lingkari nomor Mintermnya yang sesuai dengan outputnya.

4. Jika 2 Mintermnya dalam satu kolom dilingkari, maka input Mux adalah 1 dan sebaliknya input Mux adalah berlogika 0

5. Jika nomor Mintermnya hanya dilingkari pada salah satu baris dalam kolom yang sama, maka input Mux akan berlogika sesuai dengan baris persamaan pada variabel yang diberikan.

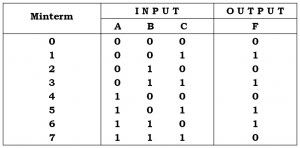

Contoh !

Implementasikan F(ABC) = ?1,3,5,6 dengan Mux (4x 1).

Jawab:

TABEL IMPLEMENTASI

GAMBAR RANGKAIAN LOGIKA

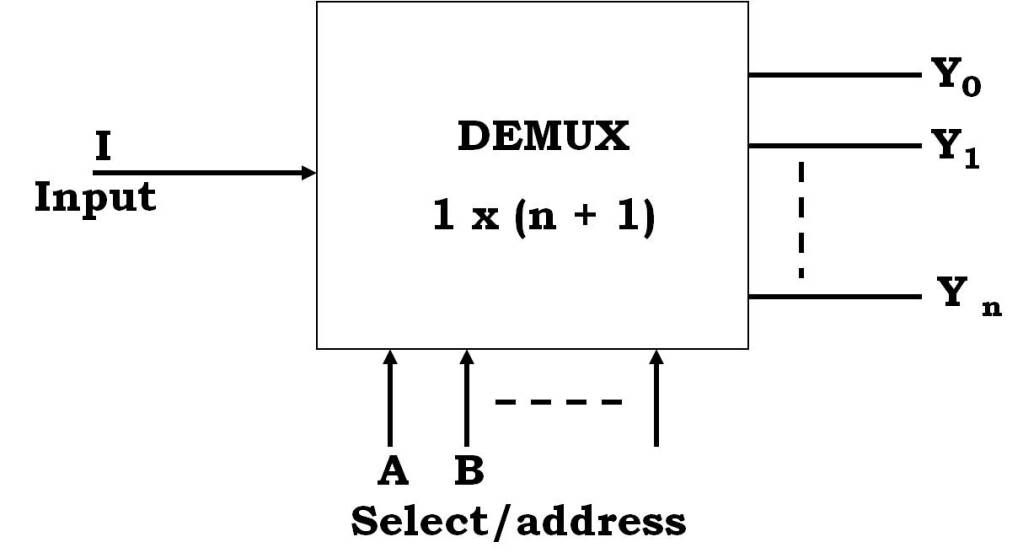

DEMULTIPLEXER (DEMUX)

22.28

22.28

-

-

1 komentar:

thx bget Brow...

ini pas bget sama tugas presentasi ku

Posting Komentar